SoW封装,到底是什么?

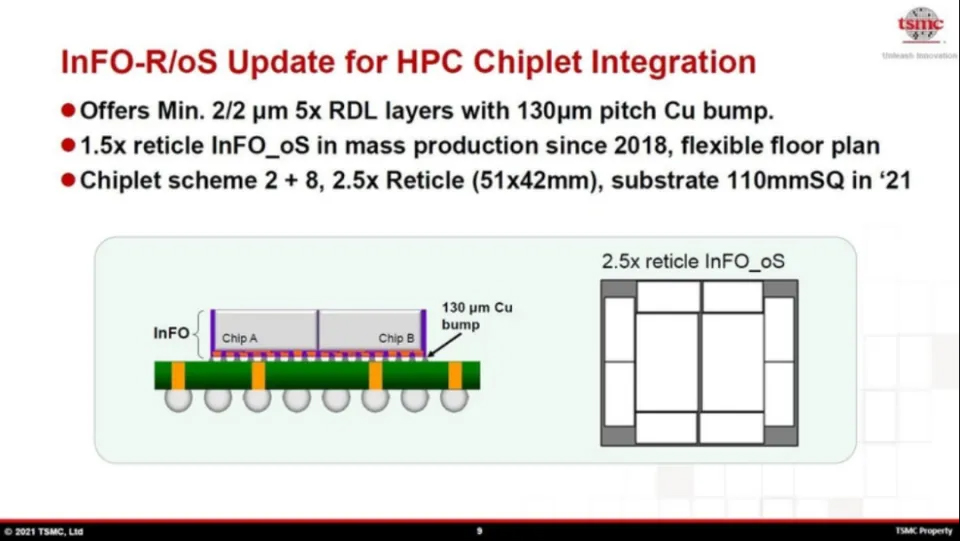

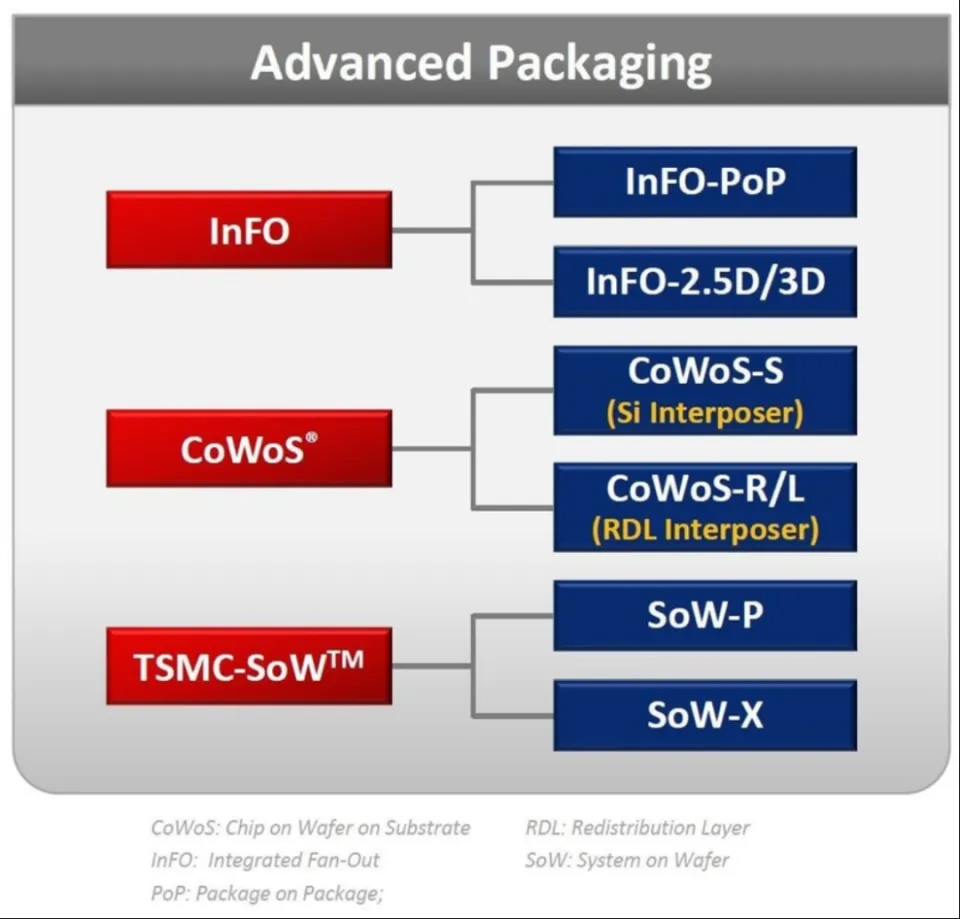

InFO技术作为低成本、高性能大封装SoW的基础,起源于台积电为移动处理器研发的小型化、薄型化封装技术InFO(Integrated Fan-Out),也被称为FO-WLP(Fan Out-Wafer Level Package)。到了2020年前后,台积电为高性能大规模逻辑芯片(如FPGA、GPU等)推出了CoWoS(Chip-on-Wafer)封装技术。该技术利用硅中介层(Si interposer)实现硅片(水平排列的芯片)之间的高密度连接。与此同时,台积电还准备并量产了InFO_oS(Chip-on-Wafer-on-Substrate)封装技术,通过InFO技术实现硅片之间的高密度连接,以作为高性能大规模逻辑的低成本封装方案。InFO_oS的优势在于其尺寸扩展相对简便,并且通过为封装基板选择InFO的RDL(重布线层),可以制造出超多层布线板。自2018年起,台积电开始量产尺寸为其光罩尺寸1.5倍的InFO_oS。

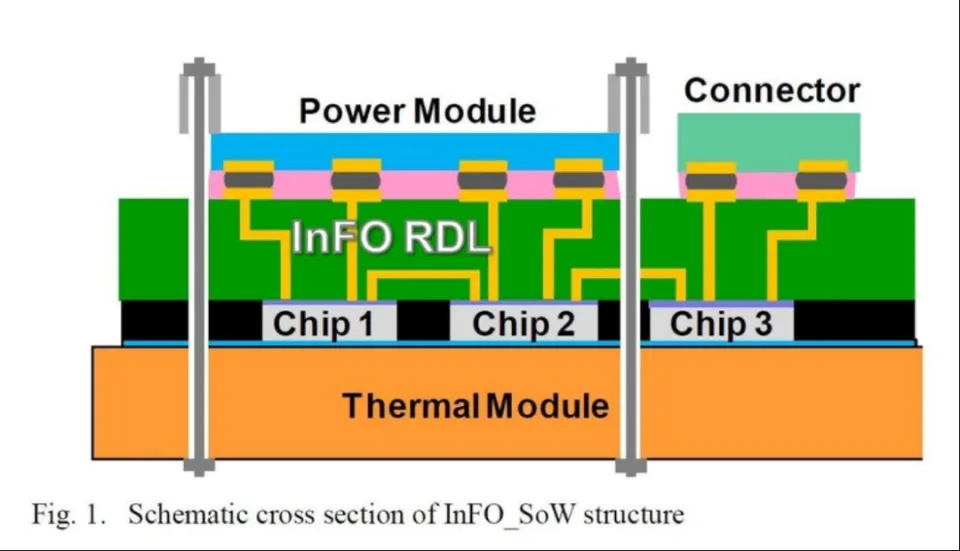

InFO_SoW(晶圆级扇出型封装系统级封装)技术是在InFO_oS(晶圆级扇出型封装)基础上发展而来的先进封装技术。它的核心特点在于将基板的尺寸,即RDL(重新分布层)的尺寸,扩展到直径300毫米的硅晶圆尺寸。这种扩展为更高的集成度和更优良的性能表现提供了可能。

在InFO_SoW的技术架构中,精细的高密度RDL被扩展至整个晶圆尺寸,这为多个硅芯片的集成提供了充足的空间。众多硅芯片以面朝下的方式(即硅芯片的电路面朝向RDL)放置在RDL上,这种布局有助于缩短信号传输距离,降低信号损失,从而提高系统的运行速度和效率。

此外,通过将电源模块和包含输入/输出IC的连接器安装在放置硅芯片的RDL背面,可以进一步构建出功能强大的系统模块。这种设计不仅优化了电路布局,还极大地提高了系统的可靠性和稳定性。InFO_SoW技术通过其创新的封装方式,显著提升了芯片的性能和集成度,为现代电子设备的小型化和高性能化发展提供了强有力的技术支持。

人工智能硬件开发商Cerebras Systems(以下简称 Cerebras)已将InFO_SoW技术应用于其深度学习加速器WSE(晶圆级引擎)。WSE技术概述于2019年8月举行的高性能处理器技术国际会议Hot Chips上发布,该技术在会议上一经亮相,便在高性能处理器开发界引起了巨大轰动。WSE以其独特的设计理念和卓越的性能表现,颠覆了传统处理器的发展模式,为人工智能领域带来了新的可能性。该公司还于2019年8月19日在新闻稿中正式宣布了WSE的开发,进一步巩固了其在人工智能硬件市场中的领导地位。WSE的推出,不仅展示了Cerebras在技术创新方面的强大实力,也为整个行业树立了新的技术标杆。相信在不久的将来,WSE将在更多领域发挥重要作用,推动人工智能技术的不断前进。

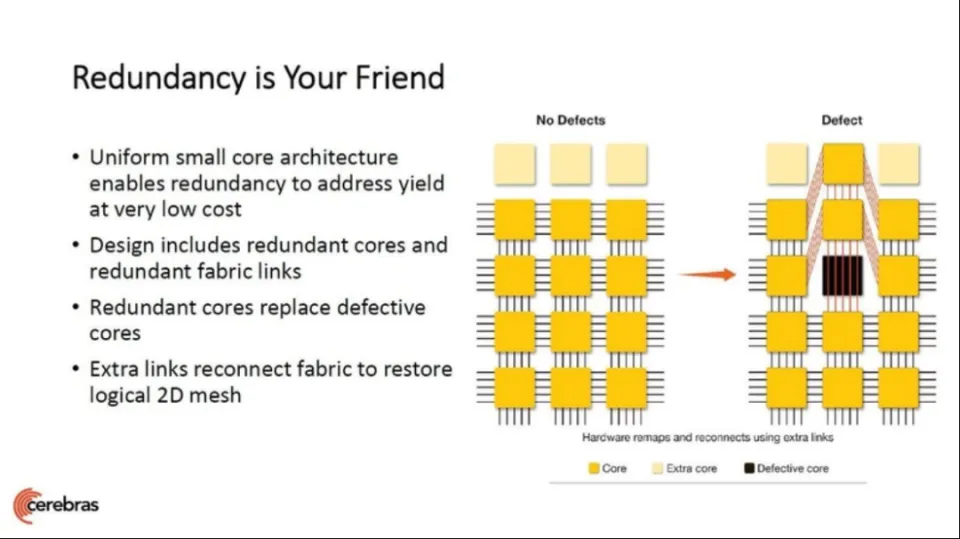

InFO_SoW和WSE技术不同,主要在于处理硅片的方式。InFO_SoW技术将不同制造技术的小芯片安装在RDL上,而WSE技术在300毫米硅晶圆上制造84个微型芯片。这些芯片通过划线连接,呈方形。AI处理器核心级测试后,有缺陷的芯片会被移除并替换为冗余芯片,布线布局在测试后确定。

这仅仅是一个猜测,但他们可能会制作一块略大于微型芯片组的方形RDL板,或者将预制的RDL板连接到微型芯片组上。这种设计的精妙之处在于其尺寸的把控,RDL板的尺寸为215毫米见方,而其外接圆直径为304毫米,这一尺寸略大于300毫米晶圆,为后续操作提供了更多的灵活性和空间。

Cerebras发布的WSE照片中包含了RDL板,上面布满了许多通孔。这些通孔的设计并非无的放矢,它们被认为是用来机械连接上下电源模块、连接器和冷却板的。这种设计确保了各个组件之间的稳固连接,同时为电流的顺畅流通和散热提供了保障,从而提高了整个系统的稳定性和性能。

InFO_SoW技术在WSE的三代产品中得到了持续的应用。Cerebras于2019年8月首次发布了WSE,这一创新产品在业界引起了巨大的轰动。随后,他们在2021年4月发布了第二代晶圆级处理器WSE-2,这一代产品在性能上有了显著的提升。紧接着,在2024年5月,第三代晶圆级处理器WSE-3问世,再次刷新了人们对于处理器性能的认知。这两代产品均采用了台积电先进的制造工艺,这无疑为产品的卓越性能提供了坚实的保障。

通过持续的技术创新和工艺优化,Cerebras在晶圆级处理器领域不断突破,为人工智能、高性能计算等前沿领域的发展提供了强大的硬件支持。他们的成果不仅展现了半导体技术的巨大潜力,也为整个科技行业的发展注入了新的活力。

台积电目前正在积极开发名为SoW-X(意为“极致”)的下一代InFO_SoW技术,旨在推动芯片性能达到新的高度。同时,该公司近期对先前研发的InFO_SoW技术进行了命名调整,将其更名为SoW-P,以更好地体现其在先进封装技术领域的持续创新与拓展。

SoW-P 和 SoW-X 的区别在于,前者分布在同一处理器上,而后者分布在处理器(或 SoC)和内存模块上。这种分布方式的不同,直接影响到了两者在性能、功耗以及适用场景上的差异。

SoW-P 由于将所有组件集中在同一处理器上,因此其设计更加紧凑,适用于对空间要求较高的应用场景,如移动设备或嵌入式系统。这种设计在提高集成度的同时,也简化了系统架构,使得数据传输路径更短,从而降低了延迟并提升了系统响应速度。然而,这种高度集成的方式也带来了散热方面的挑战,并且在扩展性上相对受限。

相比之下,SoW-X 将处理器(或 SoC)和内存模块分开分布,这种设计提供了更好的可扩展性和灵活性。它允许根据具体需求独立扩展处理器或内存模块的容量和性能,适用于对计算资源和内存需求不断增长的高性能计算、数据中心等领域。此外,这种分布方式也有助于散热管理,因为关键组件可以更均匀地分布在主板上,从而降低局部过热的风险。但与此同时,这种设计也增加了系统复杂性和成本,因为需要更复杂的互连架构来确保处理器和内存模块之间的高效通信。

总体而言,SoW-P 和 SoW-X 各有优势,适用于不同的应用场景。SoW-P 更适合对集成度和响应速度有较高要求的场景,而 SoW-X 则更适合对扩展性和性能可定制化有较高需求的场景。